# 72 CHANNEL 125 MSPS ADC STATUS

G. VISSER

INDIANA UNIVERSITY CYCLOTRON FACILITY

8/22/2008

1 (Gerard Visser – Hall D Online Meeting 8/22/2008)

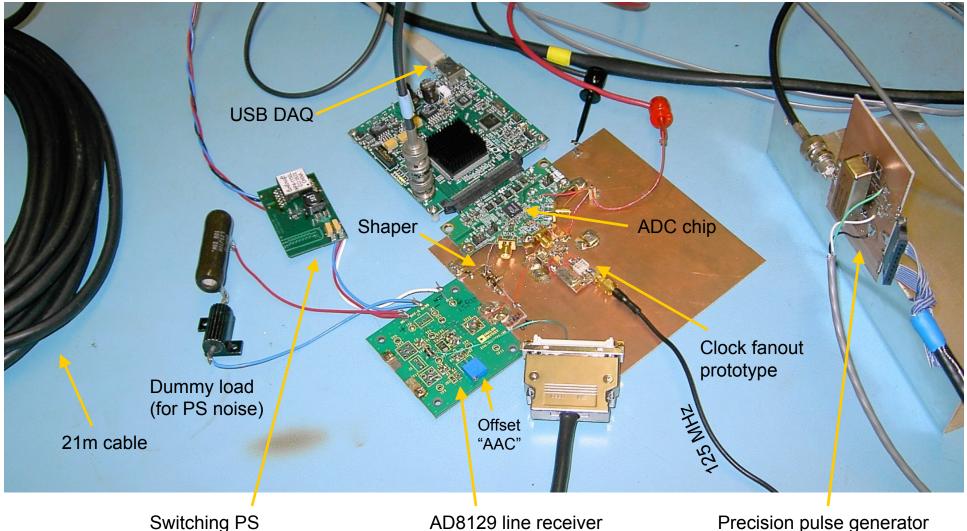

# The development prototype (single channel)

Presently has essentially the real implementation of line receiver, eq, shaper, ADC, clock fanout, PS for line receiver. Missing: Offset DAC (not needed), ADC PS (should do), FPGA (not needed).

$24V \rightarrow \text{isolated } \pm 5.5V, 18W$

AD8129 line receiver with equalization circuit

Precision pulse generator (mercury reed relay)

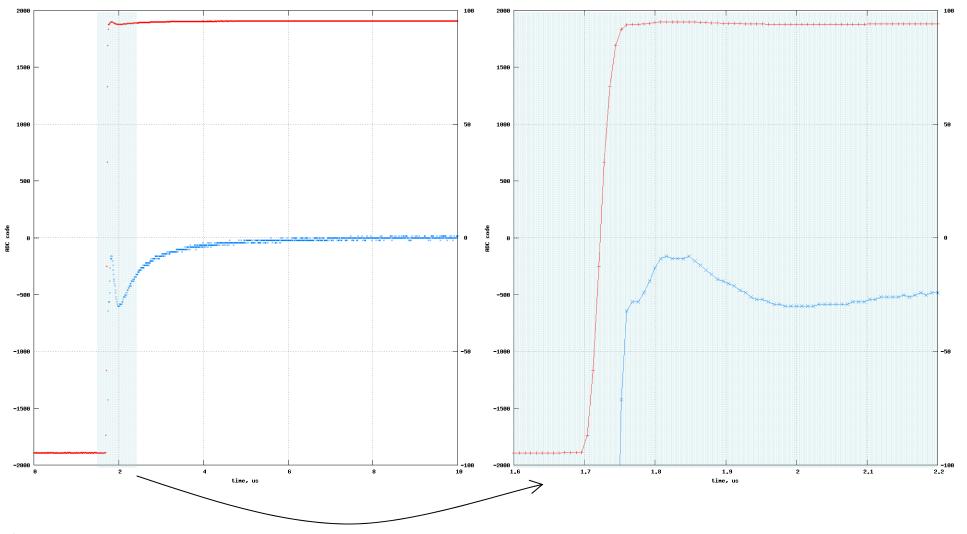

# **Step response of cable – ADC system**

OUR GOAL: Provide a faithful measurement of the signal driven by the ASIC, i.e., into terminated cable / ADC system

$\bullet$  Settles to <1% in 60 ns – if cable temperature is held within ± 5  $^\circ\text{C}$

• Peaking time  $\approx$  28 ns for impulse input (about  $\frac{1}{2}$  the step risetime shown here)

<sup>3 (</sup>Gerard Visser – Hall D Online Meeting 8/22/2008)

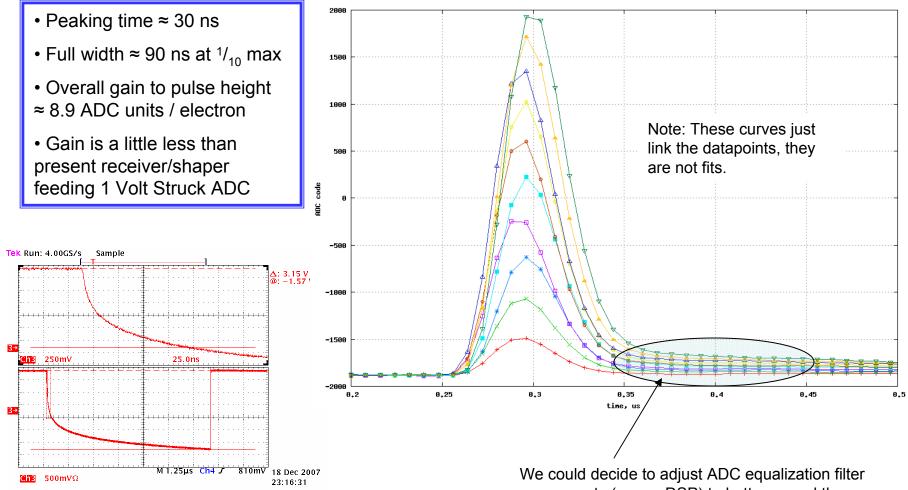

#### **Detector-equivalent pulse response of ASIC – cable – ADC system**

47 to 470 electrons, assuming  $5 \times 10^4$  gain and t<sub>o</sub> = 1.38 ns

Input test pulse to capacitor, as in GlueX-doc-931

We could decide to adjust ADC equalization filter components (or use DSP) to better cancel the remaining tail. Decide it later, after some testing with detectors / GAS-2 / ADC. Remember, (PVC) cable temperature also affects the tail.

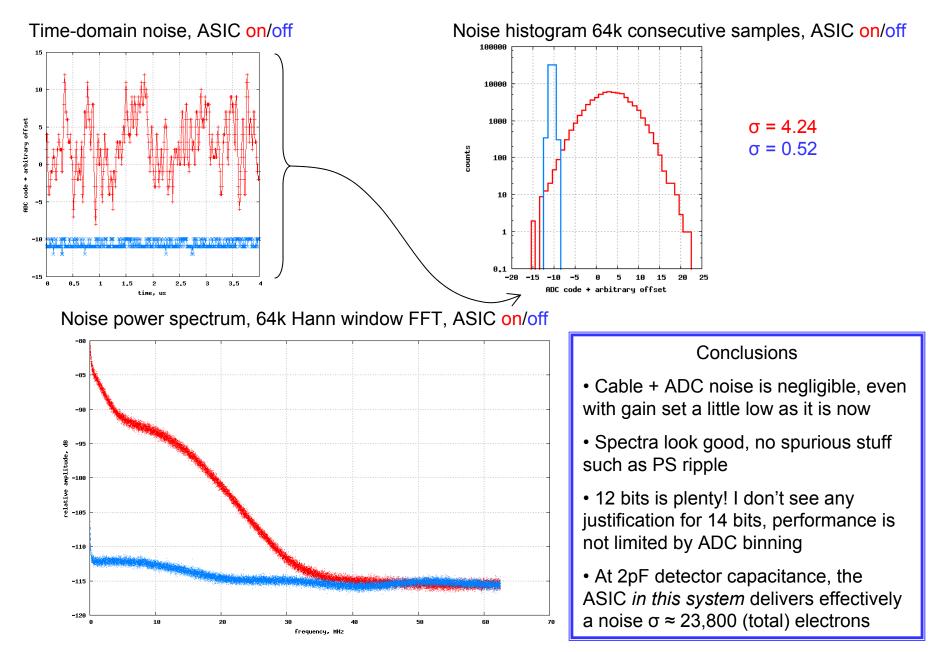

#### Noise

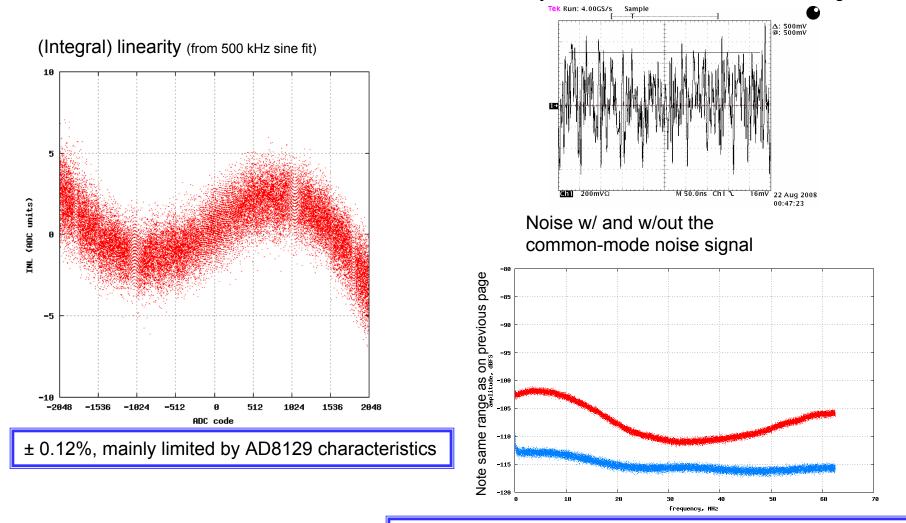

#### **Linearity and Common-Mode Rejection**

Inject a harsh common-mode noise signal:

That much common-mode noise contributes only about as much as the ASIC noise with no detector capacitance – good!

## What will be the production test plan?

Some highlights:

- All supply voltages probed, input supply currents monitored (+5, +3.3, ±12 from backplane)

- DC transfer function (including linearity and missing-codes check), each channel, offset DAC  $\rightarrow$  ADC

- Noise histogram, each channel

• Connect to input test fixture, standard pulse (step?) response check on each channel, synchronous to clock, i.e. tests also for clock problems.

• Data integrity checks from read/write test patterns and push test patterns to output FIFO

The above will be done at a semi-automated test station consisting of:

- VXS crate (JLab?) including CPU and trigger/clock source (VXS)

- Current monitor VME extender

- Perhaps an external computer to run the test software, at least something for operator interface

- Three plug-in test source modules, probably also involving a signal generator

- Benchtop DMM

- Other test equipment will of course be needed (and available) for diagnosis and repair...

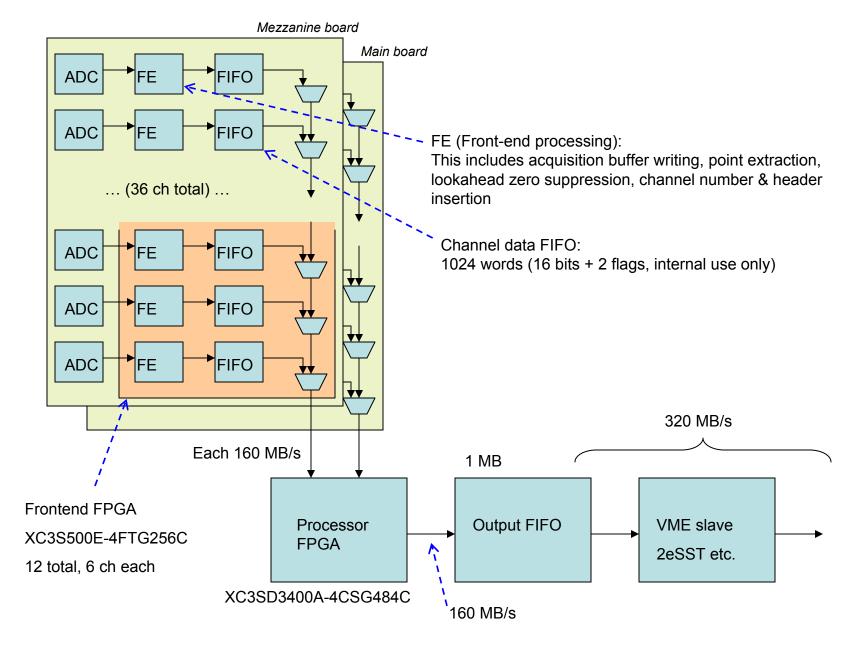

#### **Reminder / update on the ADC board datapath architecture**

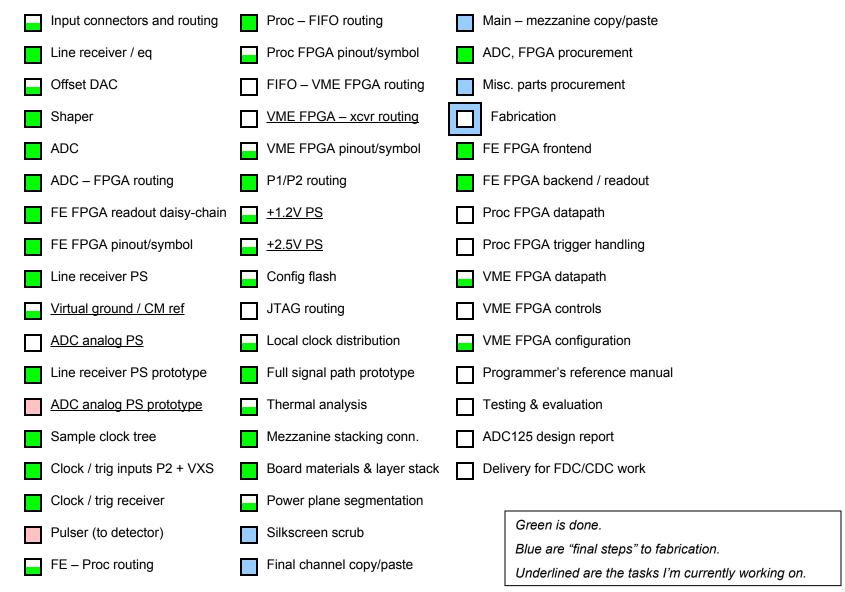

# Status of the ADC125 design work

We were supposed to have a module by this time... Where is it?

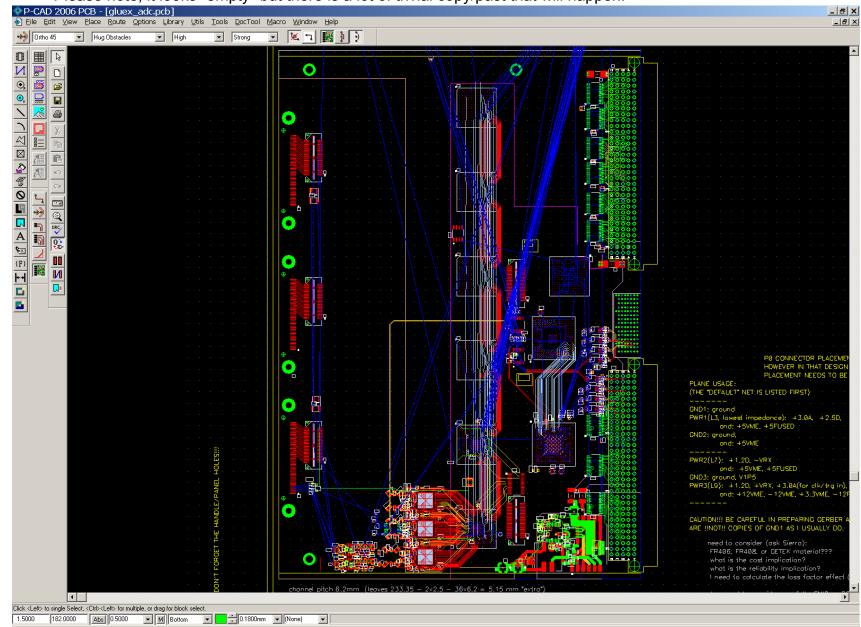

## The mainboard layout today

Please note, it looks "empty" but there is a lot of trivial copy/past that will happen!

10 (Gerard Visser – Hall D Online Meeting 8/22/2008)

## **Contract status**

It started about 10/7/2007 (according to my IUCF effort reporting)

As of this week:

- Labor 520 hours 51% of budget (1015 hours)

- Materials \$10,094 (including \$6,791 for ADC chips) 39 % of budget

Performance: Average (over whole period) time committed  $\approx 32\%$  – is 64% of planned

Recently, 104 / 185 hours

I can offer excuses from other projects, of course, but that is not all so helpful...

Billing status:

- Should have billed some time ago, but...

- IU accountants mistakenly applied overhead although it was supposed to be waived for this project as a capital construction effort...

- Then they realized it and have taken an inappropriately long time to fix it...

- Because of all that, they haven't yet sent a bill...

- I am told that one will be sent by about 9/8