# Hall A Moller Polarimeter DAQ Upgrade

**B.** Sawatzky

CNU 12 GeV Trigger Workshop July 8, 2010

# Overview

- Brief description of the Hall A Moller

- What do we gain from the DAQ upgrade?

- What does the DAQ upgrade involve?

- Hardware description

- Capabilities

- Trigger definitions

- Some results

- Online histograms, rate comparisons, etc.

- Miscellaneous comments

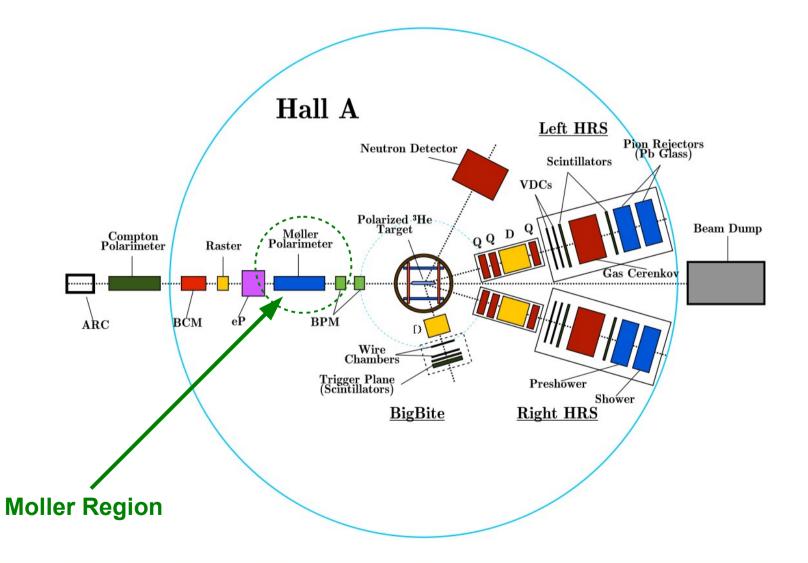

### Hall A Overview

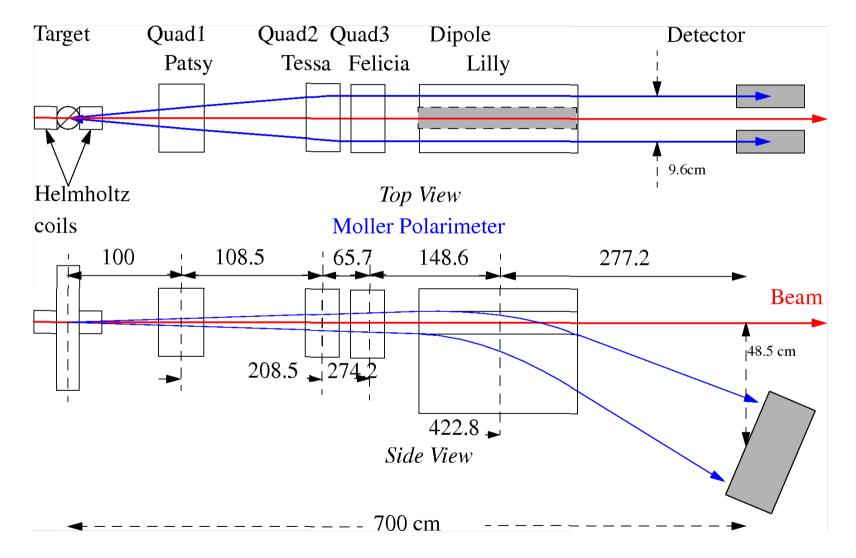

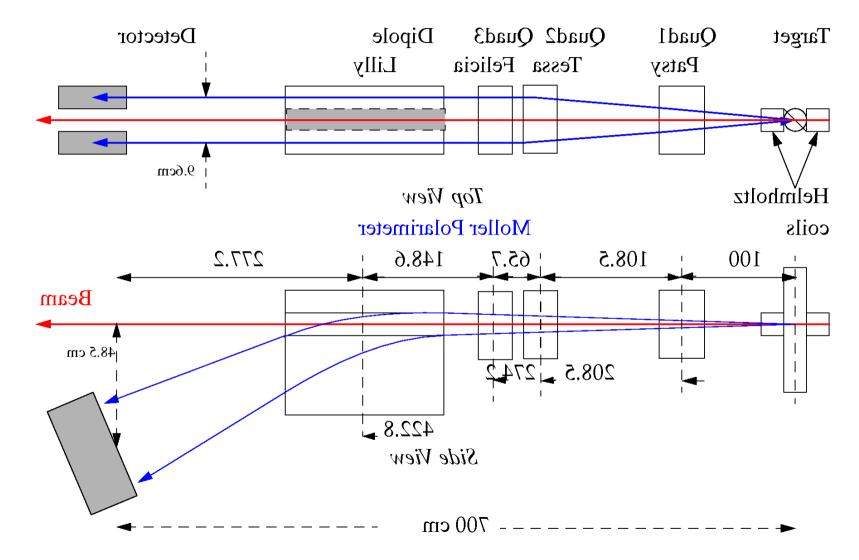

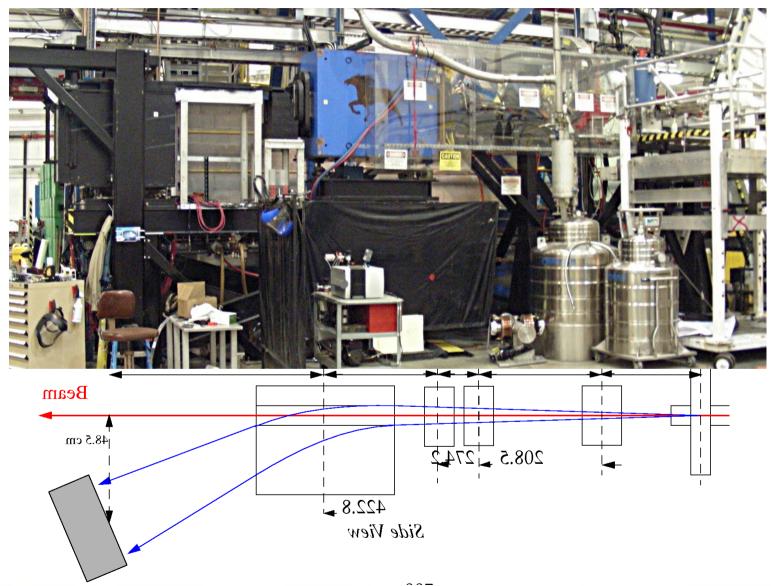

### **Moller Hardware**

### **Moller Hardware**

**Moller Hardware**

# Why do we want the DAQ upgrade?

- Help improve the systematic error from  $2\% \rightarrow 1\%$

- FADC data grants full information about detector systematics/performance

- Negligible DAQ deadtime (pipelined design)

- Intrinsic HW deadtime (ie. pile-up) can be trivially identified/measured using sample data

- Replace old/obsolete DAQ hardware

- existing DAQ is 12 years old, no spares, rate limited

- FADC design is fast & flexible

- Accommodate the new segmented aperture detector

- 8 paddles (4 per arm) instead of 2

- present aperture paddles overload at > luA

### What is involved in the DAQ Upgrade?

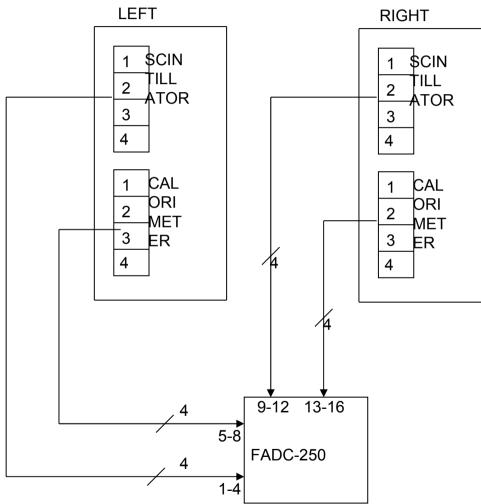

- System built around a JLab F250 Flash ADC

- 16 analog inputs (8 calo. blocks, 8 scint. paddles)

- 4 ns sample time, 12 bits/sample resolution

- FPGA device → flexibility of software with the speed and response time of hardware

- Custom FADC firmware

- FADC generates our triggers, no signal splitters, discriminators, or summing modules needed

- Thresholds, sample windows, trigger prescales all software controlled

- Fairly straight forward to add new features to the firmware (turn around on the order of a week)

### What is involved in the DAQ Upgrade?

- Also some auxiliary support modules (read out during every MPS interval)

- CAEN v560 scaler (16 channels)

- BCM, Moller target position, 100 kHz clock

- (plus redundant counters for cross checks)

- CAEN v792 QDC (16 channels)

- MPS, QRT, HEL flags

- (plus redundant data for cross checks)

- Easy to add/read other modules if needed

### What is involved in the DAQ Upgrade?

- New dedicated DAQ computer: hamoller.jlab.org

- fast, modern machine: 4 CPU cores, 2TB of RAID10 storage for local data and scratch

- shares adaqfs file system, usual accounts

- goal is to support zero-deadtime streaming data from DAQ at full 160kHz coincidence rate (no prescaling) → sustained ~50 MB/sec

- ROOT-based analyzer using PODD (Hall A analyzer framework)

- new decoding routines added to handle FADC

- still a work in progress, but quite functional

# Photo of old DAQ electronics

12 GeV Trigger Workshop • July 8, 2010

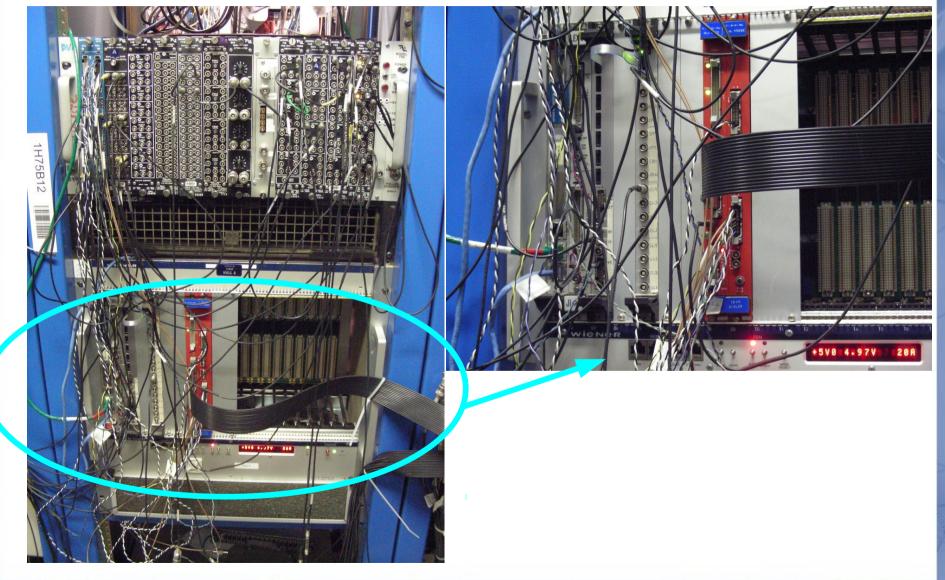

## Photo of new DAQ rack

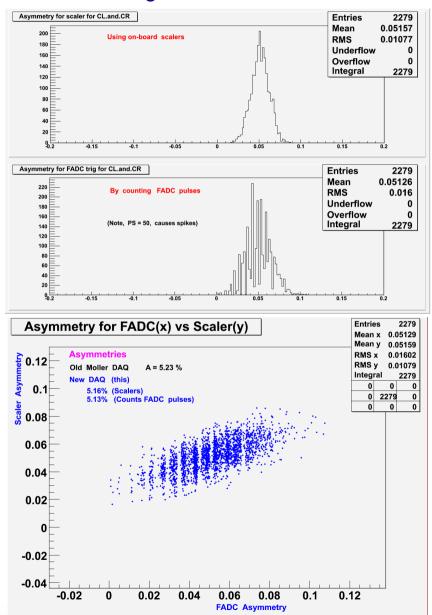

#### FADC internal trigger criteria:

$CR = \sum_{I=1,4} \sum_{j=1,2} P_{I}^{J} > threshold$

$$\begin{aligned} \text{CL} &= \sum_{i=1,4} \sum_{j=1,2} \text{P}_{i}^{J} > \text{threshold} \\ \text{SL} &= (\sum_{J=1,2} \text{S1}^{J} > \text{thr}) \text{ or } (\Sigma J = 1,2 \text{ S2}^{J} > \text{thr}) \text{ or} \\ &\quad (\Sigma J = 1,2 \text{ S3}^{J} > \text{thr}) \text{ or } (\Sigma J = 1,2 \text{ S4}^{J} > \text{thr}) \end{aligned}$$

SR =  $(\Sigma_{J=1,2} S5^{J} > thr)$  or  $(\Sigma J=1,2 S6^{J} > thr)$  or  $(\Sigma J=1,2 S7^{J} > thr)$  or  $(\Sigma J=1,2 S8^{J} > thr)$

#### 'DATA' Trigger (OR of 'internal' trigger cond:):

CL.AND.CR prescaled from 1 to 2000 CL prescaled from 1 to 2000 CR prescaled from 1 to 2000

#### Information recorded:

- digitized waveforms

- helicity state

- status counters, etc.

#### 'HELICITY' Trigger (external trigger):

MPS leading edge (30 – 2000 Hz)

#### Information recorded:

- Helicity, MPS, QRT states, BCM,

- Moller Target ladder position information,

- 100 kHz clock,

- status counters, etc.

- FADC 'Software' scaler data:

- CL singles, CR singles

- CL and CR

- CL and SL

- CR and SR

- CL and CR and SL and SR

- CL and CR and (SL and SR delayed > 100 ns)

# FADC Moller DAQ Trigger Types

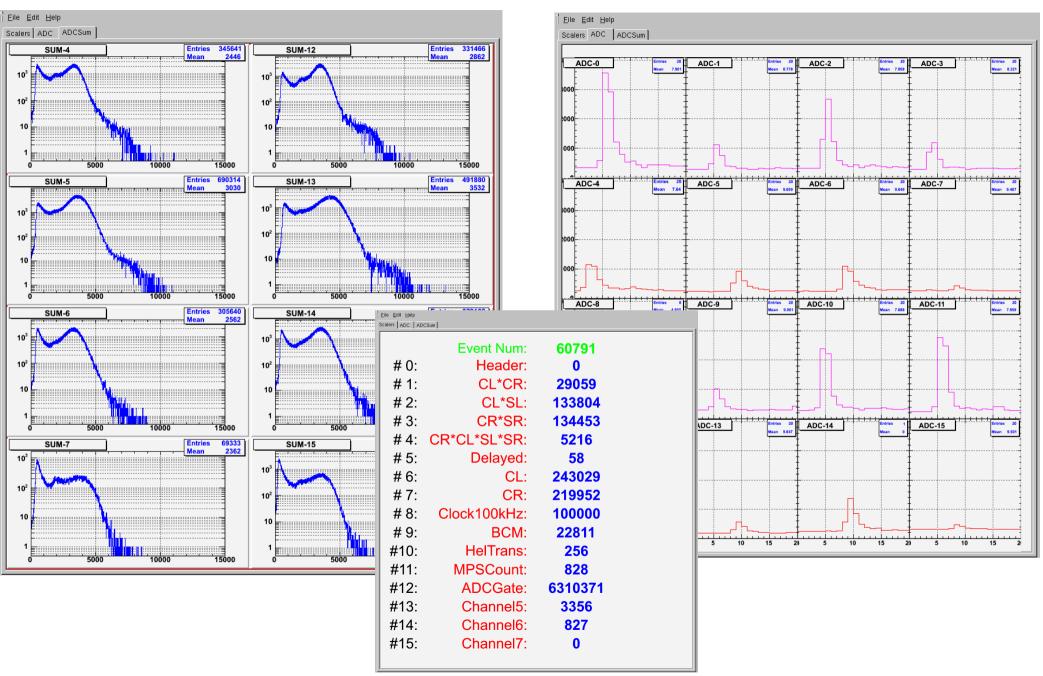

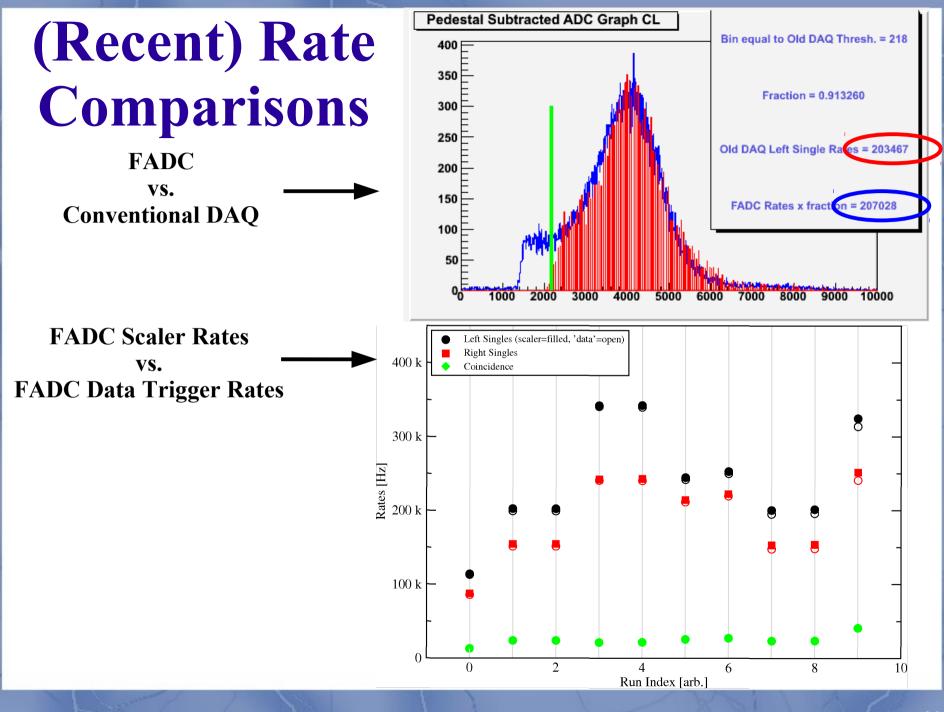

## **On-line FADC monitor**

12 GeV Trigger Workshop • July 8, 2010

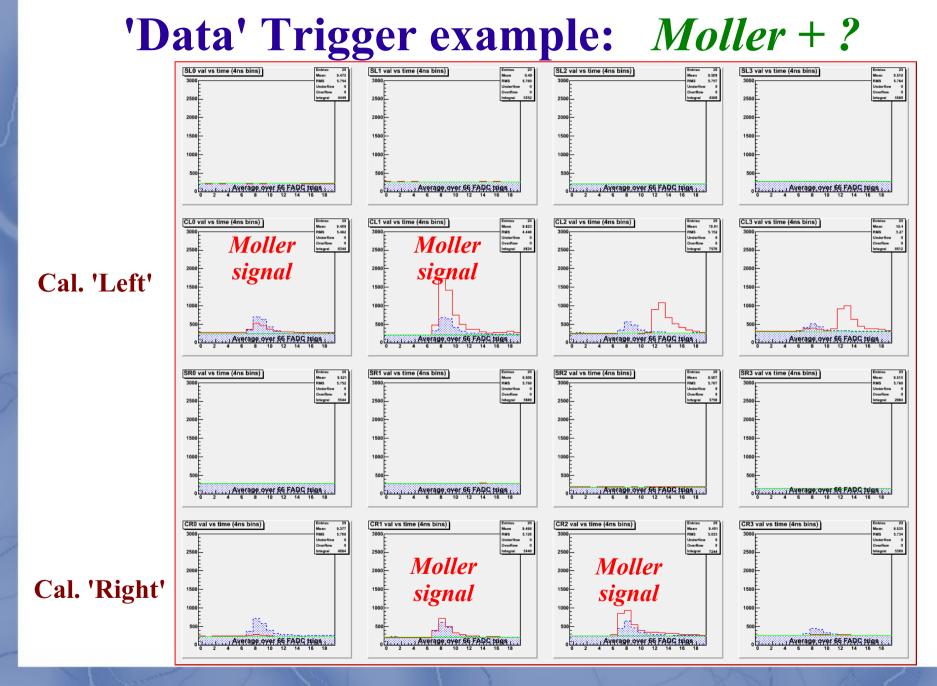

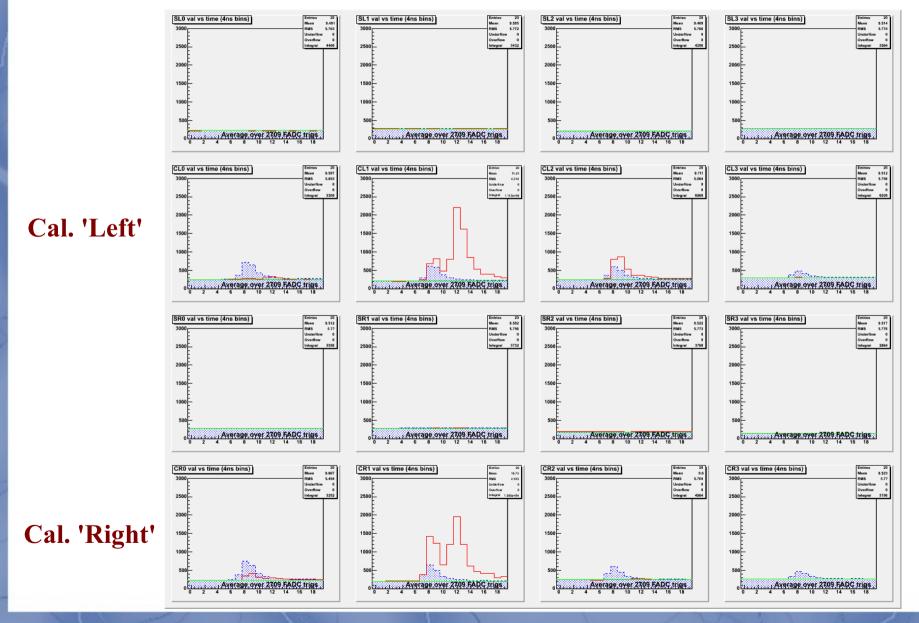

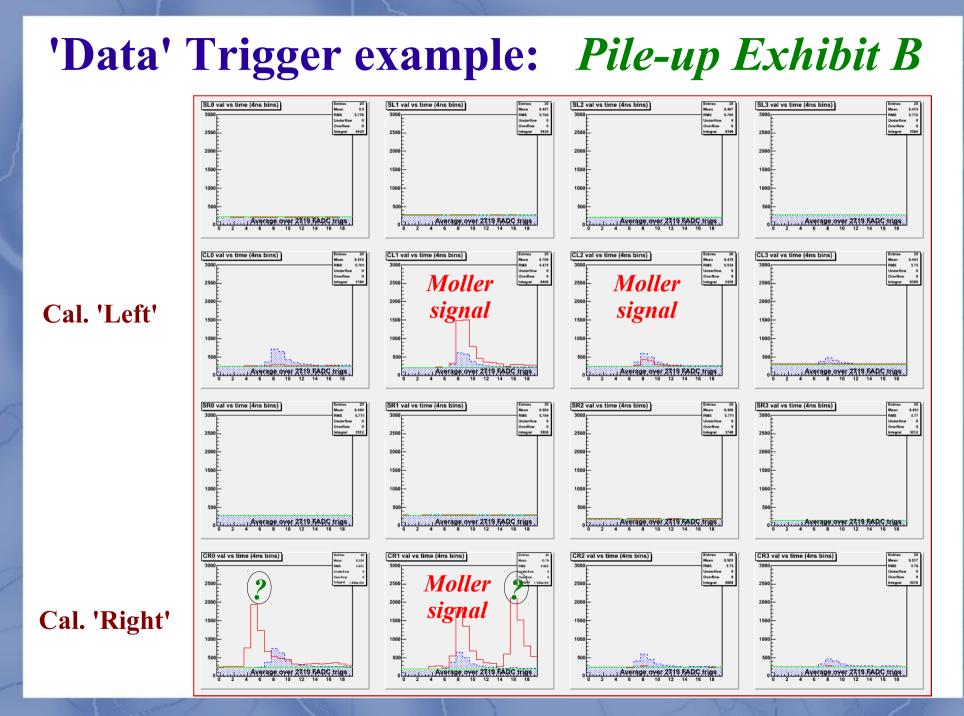

### 'Data' Trigger example: *Pile-up Exhibit A*

12 GeV Trigger Workshop • July 8, 2010

12 GeV Trigger Workshop • July 8, 2010

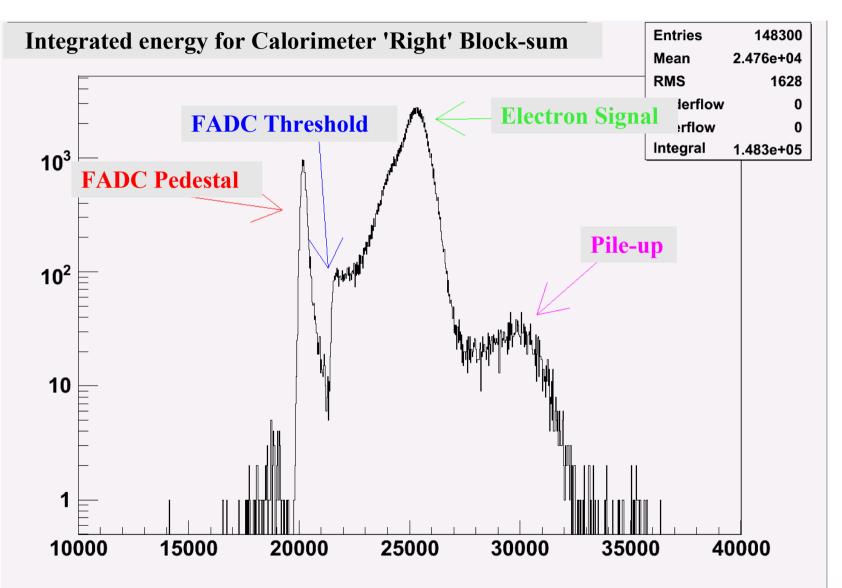

# **Total Energy Histogram**

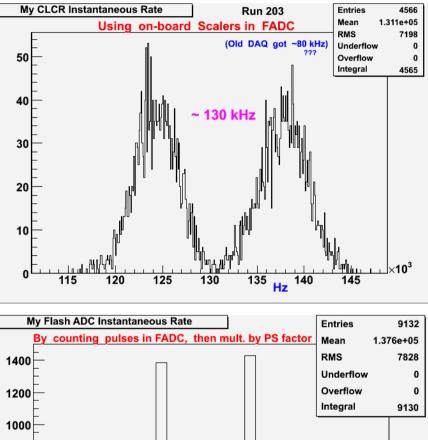

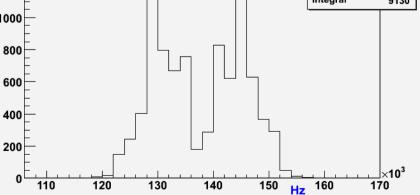

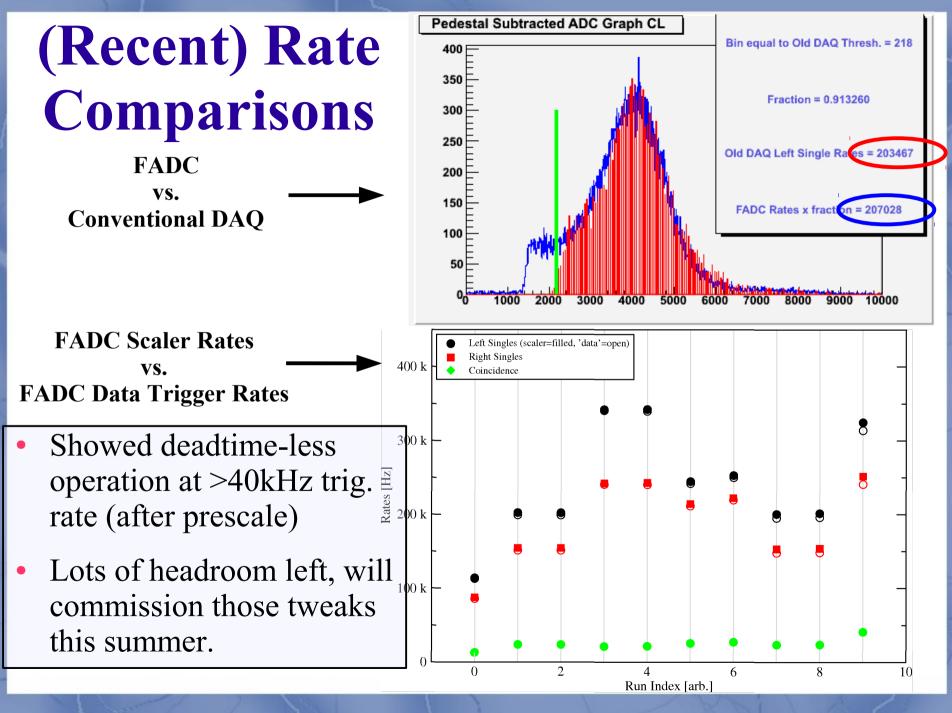

### **Rates and Extracted Asymmetries**

12 GeV Trigger Workshop • July 8, 2010

## **Miscellaneous Comments**

- Ran across several interesting features in the FADC that ultimately required firmware updates

- not unexpected; support from DAQ and Fast Electronics group was great!

- need to factor in this debug time and additional load on the experts during 12 GeV commissioning

- Radiation Hardness during *PREx* (probably worst-case scenario)

- FADC250 seemed to survive OK, but

- MVME v6100 CPUs didn't fair very well

- needed fairly frequent reboots

- lost 2 of them in two weeks of high-luminosity running (they were upstream, and well shielded too, at least by historical standards)

- Wishlist item:

- Generic library to decode blocked FADC data → serialized CODA (evio) event stream

- (perhaps impossible to provide general solution...)